In Parallel In Serial Out (PISO) shift registers, the data is loaded onto the register in parallel format while it is retrieved from it serially.Figure 1 shows a PISO shift register which has a control-line. Module Parallelinserialoutloadenablebehavior(input Clk, input ShiftIn, input 3:0 ParallelIn, input load, input ShiftEn, output ShiftOut, output. The following code models a four-bit parallel in shift left register with load and shift enable signal. 4 Bit Sipo Shift Register Vhdl Code Vhdl code for 4 bit shift register allaboutfpgacom, vhdl code for shift register can be categorised in serial in serial out shift. Bit serial arithmetic Vs Digit serial Arithmetic.

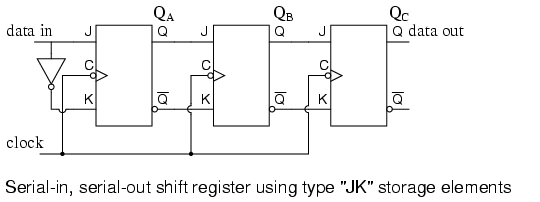

Need vhdl code for 16 bit serial-in, serial-out shift register. Write the above code for left shift in place of right shift. Repead the testbench and verification for N=4 2. In test bench the shift register is instantiated with N=2. The testbech for the Serial shift register Serial Input Serial Output Shift Register Exercizes 1.

0 Comments

Leave a Reply. |

RSS Feed

RSS Feed